This tiny chip could single-handedly solve the RAM shortage by allowing hyperscalers to reuse old DDR4 memory via CXL — and it comes with an extraordinary feature

It's promising, but the lack of latency confirmation raises huge questions

- Marvell Structera X 2404 allows the reuse of DDR4 without buying new DRAM

- Twelve DIMMs per controller deliver 1.5TB physical memory capacity

- Memory compression effectively doubles usable capacity using LZ4 at line rate

Hyper-scalers under pressure from rising memory prices could turn to decommissioned DDR4 modules as a practical resource.

The Marvell Structera X 2404 is a CXL-based memory expander designed to make the reuse of DDR4 modules viable at large scale.

When operators install 128GB units pulled from retired systems, the controller delivers up to 1.5TB of physical capacity without the need for new DRAM.

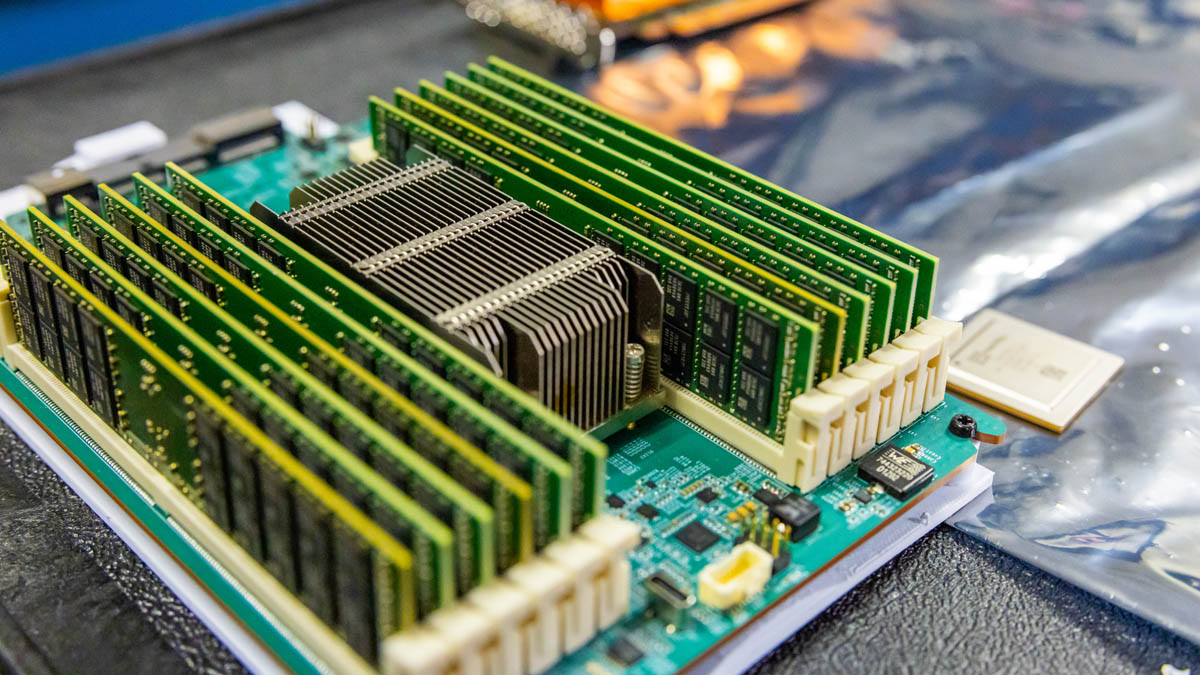

Article continues belowDeployment layout of Structera X 2404

The Structera X 2404 fits into standard data center server racks as a PCIe-attached device rather than a traditional DIMM, so it operates as an external memory resource.

It supports four DDR4 channels and allows three DIMMs per channel, which creates a total of twelve modules attached to a single controller.

This approach appeals to hyperscalers because of the vast quantities of older modules stored from previous upgrade cycles.

It also reduces manufacturing needs because only the controller, board, and cable require production, not the DRAM itself.

Sign up to the TechRadar Pro newsletter to get all the top news, opinion, features and guidance your business needs to succeed!

The DDR4 model focuses on cost, but some operators need more performance than older modules can deliver.

The Structera X 2504 serves those environments and uses DDR5 RAM across four channels.

It connects through CXL 2.0 over PCIe Gen5 and delivers more bandwidth because it bypasses the CPU’s memory channels.

This design appeals to deployments that require faster throughput while still seeking expansion beyond the limits of the processor’s DDR5 DIMM slots.

The standout capability in both devices is memory compression, which changes how capacity is delivered and priced.

Marvell uses LZ4 at line rate, and it reports ratios between 1.8x and 2x during normal operation. This means a 1.5TB capacity can scale to as much as 3TB.

This approach allows hyperscalers to treat reused DDR4 as a larger and cheaper pool than its physical size suggests.

It also reduces pressure on DDR5 supply chains because systems can rely on compressed expansion rather than purchasing additional modules.

That said, latency remains the main concern because independent testing under real workloads has not yet occurred.

CXL already introduces extra delay, and compression adds more uncertainty when memory access becomes unpredictable.

Without third-party testing of random read latency, it remains unclear whether these devices perform well under scattered access patterns.

Random reads affect many production systems, and slow responses can wipe out the advantages of added capacity.

This uncertainty represents the largest technical risk because latency determines whether the expansion behaves like real memory or a slower tier.

Via ServeTheHome

Follow TechRadar on Google News and add us as a preferred source to get our expert news, reviews, and opinion in your feeds. Make sure to click the Follow button!

And of course you can also follow TechRadar on TikTok for news, reviews, unboxings in video form, and get regular updates from us on WhatsApp too.

Efosa has been writing about technology for over 7 years, initially driven by curiosity but now fueled by a strong passion for the field. He holds both a Master's and a PhD in sciences, which provided him with a solid foundation in analytical thinking.

You must confirm your public display name before commenting

Please logout and then login again, you will then be prompted to enter your display name.

Become a TechRadar Insider

Become a TechRadar Insider