AMD breaks 1GB L3 cache barrier with new EPYC processors

AMD has gone public with a new server CPU roadmap

Sign up for breaking news, reviews, opinion, top tech deals, and more.

You are now subscribed

Your newsletter sign-up was successful

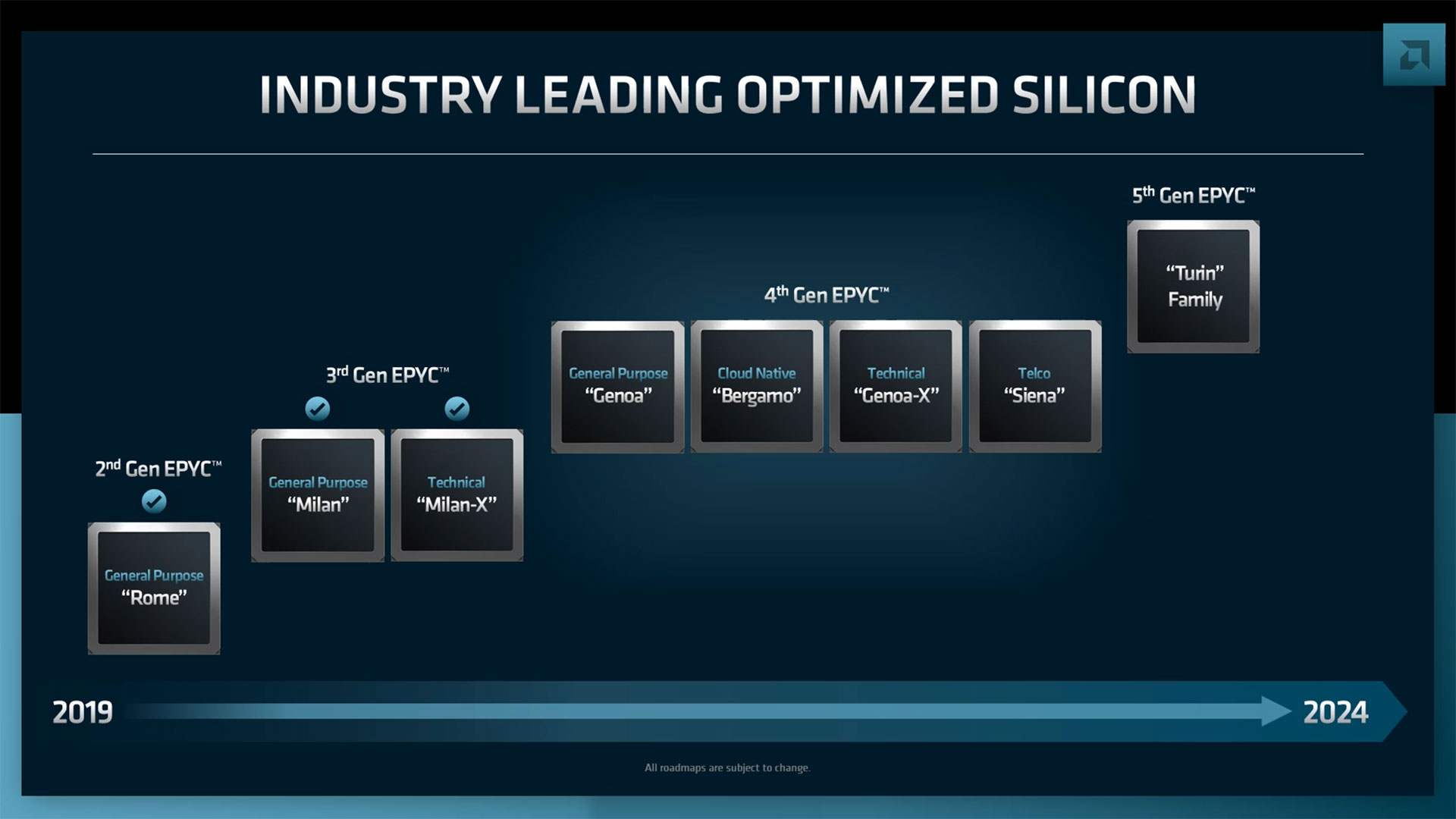

AMD has published an updated roadmap for its line of EPYC server processors, extending until the end of 2024.

During a presentation for investors, the company revealed that its fourth-generation EYPC chips are on track to launch in 2023. The range will also benefit from two new additions: Genoa-X, equipped with 3D V-Cache and optimized for technical computing workloads, and Siena, targeted at edge and telecoms use cases.

AMD went on to tease new EPYC chips based on its Zen 5 architecture, codenamed Turin, which promise a significantly larger generation-on-generation performance increase courtesy of a complete redesign. These fifth-generation chips are scheduled to come to market within the next two years.

Article continues below

AMD EPYC Genoa-X and Siena

Although AMD remained tight-lipped on the specs for its upcoming Turin chips, the firm did dive deeper into the new additions to its fourth-generation EPYC portfolio.

Genoa-X will fill the same gap in the lineup as Milan-X chips, taking advantage of advanced die-stacking technology (3D V-Cache) to offer upwards of 1GB L3 cache per socket, more than any x86-based chip currently on the market.

This will make them ideally suited for workloads that rely on large quantities of data, such as computational fluid dynamics and structural analysis. AMD has previously described these workloads as essential for “companies that must model the complexities of the physical world” to inform the design of innovative new products.

The new Genoa-X chips will come in multiple flavors, each catering to different performance requirements, with core counts climbing as high as 96. If the previous-generation are anything to go by, they won’t come cheap.

Sign up to the TechRadar Pro newsletter to get all the top news, opinion, features and guidance your business needs to succeed!

AMD EPYC Siena chips, meanwhile, are optimized for performance per watt, which makes them the sensible choice for space-constrained edge computing scenarios and less performance-dependent telecoms use cases.

These new chips will join general-purpose EPYC Genoa chips and high-core count, cloud-optimized Bergamo processors, rounding out the lineup by covering off a full gamut of use cases.

Joel Khalili is the News and Features Editor at TechRadar Pro, covering cybersecurity, data privacy, cloud, AI, blockchain, internet infrastructure, 5G, data storage and computing. He's responsible for curating our news content, as well as commissioning and producing features on the technologies that are transforming the way the world does business.